Mobility and threshold voltage extraction in transistors with gate-voltage-dependent contact resistance

Introduction

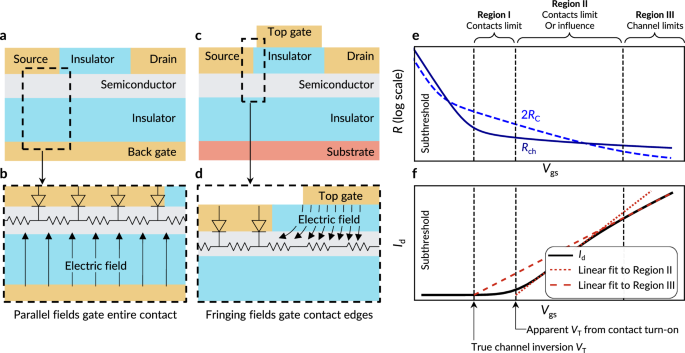

The electron and hole mobilities of emerging semiconductors are frequently estimated from measured current vs. voltage characteristics (e.g., from drain current Id vs. gate-source voltage Vgs) of field-effect transistors (FETs)1. Many such transistors have contact resistance that is a function of gate voltage due to electrostatic gate fields that affect the energy barrier and charge density at the contact/channel interface2,3. This contact gating effect is often associated with back-gated FETs (Fig. 1a), where the back gate can directly modulate the mobile charge carrier density at the contacts (Fig. 1b). However, recent work has shown that top-gated FETs (Fig. 1c) can also electrostatically control the contacts at their edges (Fig. 1d)4,5.

a Schematic of a back-gated FET, where inset b shows the parallel field from the back gate directly gating the entire contact. c Schematic of a top-gated FET, where inset d shows fringing fields gating the contact edge. (Top-gated devices without underlaps would have their contact edges gated directly by the parallel field instead.) As a result of contact gating, the channel resistance Rch and contact resistance RC can decrease at different rates as Vgs increases (e), creating a distinct kink in the resultant Id vs. Vgs characteristics (f). After exiting the subthreshold region, the channel may turn on even as the contacts remain off, suppressing Id (e, f, Region I). The contacts then turn on as Vgs further increases, leading to a sharp increase of Id (e, f, Region II). The magnitude and slope of Id here are dictated by the contacts rather than by the channel; attempting to extract the channel mobility from this region with conventional techniques can result in severe overestimation. Finally, the FET returns to a channel-limited regime when 2RC < Rch (e, f, Region III); μ can usually be safely extracted from this region. The diagrams shown here are for an n-channel FET.

Further complicating matters, the channel resistance Rch and contact resistance RC of contact-gated FETs often change at different rates (Fig. 1e), causing these devices to potentially exhibit two apparent threshold voltages: one associated with channel turn-on, and another dictated by contact turn-on6 (Fig. 1f). When the channel turns on before the contacts (i.e., at lower Vgs in n-channel FETs, as in Fig. 1e, f), Id is limited by RC and can remain low even when the channel is fully turned on (Fig. 1e, f, Region I). As Vgs increases, the contacts begin to turn on (Fig. 1e, f, Region II) before the device eventually reaches a channel-dominated regime (Fig. 1e, f, Region III), leading to a distinct kink7 in the Id vs. Vgs characteristics associated with the transition between the contact- and channel-limited regimes.

Because Id is contact-limited or contact-influenced in Region II of Fig. 1f, both Id and the transconductance (gm = ∂Id/∂Vgs) here are dominated by the contacts rather than by the channel. Thus, attempting to estimate the channel mobility (μ) using the conventional linear extrapolation method (i.e., asserting μ ∝ gm) in this region can result in severe μ overestimation3,6,7,8,9 when RC dominates and decreases as |Vgs| increases. (In the special case where RC remains constant as |Vgs| increases, the mobility can be underestimated instead.) Therefore, μ should instead be extracted from the slope of Region III in Fig. 1f (where devices are channel-limited)7,8. However, this approach is often infeasible for emerging semiconductor devices whose large RC and/or early gate dielectric breakdown can make this high-|Vgs| region hard to reach experimentally. Furthermore, when Region III of the Id vs. Vgs curve is inaccessible before dielectric breakdown (e.g., due to large RC and/or high threshold voltage |VT|), the Id vs. Vgs curve may show only a single linear region simply because the Vgs sweep ends early. For this reason, it can even be challenging to establish if a device is channel- or contact-limited based on its transfer characteristics10 alone.

To avoid μ overestimation due to contact gating, researchers can use four-terminal geometries to directly probe and subtract the voltage drop across the contacts9,11. However, care must be taken to ensure that the voltage probes are entirely non-invasive, which can be difficult in practice12,13,14,15. The Y-function method16 can also correct for mild contact gating17 but relies upon accurate VT extraction, making this method unreliable for devices that cannot access Region III6 in Fig. 1f. We demonstrate later in this work that the transfer length method (TLM) approach1 can be similarly unreliable for extracting μ from contact-gated FETs.

In this work, we propose a method for extracting the channel μ and VT of transistors that remains valid even for strongly contact-gated devices. This approach takes inspiration from the conventional TLM method1 and can analyze families of two-terminal devices that cannot access the channel-limited regime (Fig. 1e, f, Region III) in their Id vs. Vgs measurements. We validate our proposed method using synthetic data generated by a technology computer-aided design (TCAD) simulator18 and find that it accurately extracts μ even for devices where conventional methods overestimate μ by 2–3×, enabling accurate μ and VT extraction in devices with strong contact gating.

Results

Our proposed extraction is summarized in Fig. 2 and explained in detail below. We provide Python code to automate this extraction in a GitHub Repository19 and in Supplementary Section 4. Additionally, we provide a tutorial for this code in Supplementary Section 1.

We treat a contact-gated FET as a channel between gate-voltage-dependent contact resistors (a). We begin the extraction in b by performing Id vs. Vds sweeps at a fixed Vgs for a family of devices with varying channel lengths Lch. For the ith Lch, we record the Vds at which the drain current reaches a target drain current ({{{{I}}}_{{rm{d}}}={{I}}}_{{rm{d}}}^{{rm{T}}}) as ({{{{V}}}_{{rm{ds}}}={{V}}}_{{rm{ds}}}^{({{i}})}). We then plot ({{rm{V}}}_{{rm{ds}}}^{({{i}})}) vs. Lch in c and extrapolate to find the voltage drop across the contacts ΔVC. We repeat this procedure at multiple Vgs to compile the table in d (using the equations below the table to calculate the intrinsic voltages). Finally, we use data from d to prepare the plot shown in e, perform linear regression to find the slope m and y-intercept b, and extract VT = m/2 and ({{mu}}=2{{{I}}}_{{rm{d}}}^{{rm{T}}}/({{{bC}}}_{{rm{ox}}}{{W}})). We use the Monte Carlo approach described in Supplementary Section 2 to propagate error throughout the extraction in order to improve the accuracy of the extraction and to estimate standard error.

Model derivation

Here, we treat a contact-gated FET as a channel between gate-voltage-dependent source and drain resistors (Rs and Rd respectively; the total contact resistance is 2RC = Rs + Rd), as shown in Fig. 2a20. The intrinsic gate-to-source and drain-to-source biases (after considering the voltage drops across Rs and Rd) are ({V}_{{rm{gs}}}^{{prime} }={V}_{{rm{g}}}-{V}_{{rm{s}}}^{{prime} }) and ({V}_{{rm{ds}}}^{{prime} }={V}_{{rm{d}}}^{{prime} }-{V}_{{rm{s}}}^{{prime} }), where ({V}_{{rm{s}}}^{{prime} }) and ({V}_{{rm{d}}}^{{prime} }) are defined in Fig. 2a. In the linear region of an n-channel FET (({V}_{{rm{gs}}}^{{prime} } > {V}_{{rm{T}}}) and ({V}_{{rm{ds}}}^{{prime} } < {V}_{{rm{gs}}}^{{prime} }-{V}_{{rm{T}}})), Id is:

where Cox is the gate insulator capacitance per unit area, and W and Lch are the width and length of the channel. In this extraction, we build a system of equations based on Eq. (1) that we use to simultaneously solve for μ and VT. In Eq. (1), VT refers explicitly to the true channel VT associated with channel inversion (as defined in Fig. 1f); thus, this channel VT often cannot be extracted directly in contact-gated devices. [For emerging FETs with intrinsic channels (no counter-doping), such as two-dimensional (2D) FETs, the channel is considered inverted when the carrier concentration is approximately equal to the density of states at the relevant band edge21.]

To build our system of equations, we use a TLM-like approach where we consider a family of devices with various Lch (using multiple two-terminal devices or a larger TLM-like test structure). As Rs and Rd are Vgs-dependent, we use Id vs. Vds sweeps at fixed values of Vgs to ensure these resistances remain constant. Further, as Rs and Rd contain Schottky diodes, they are nonlinear circuit elements, i.e., their resistances are functions of Id. To ensure constant RC, we therefore perform the extraction at a constant current.

With these considerations in mind, we begin by choosing a target drain current ({I}_{{rm{d}}}^{{rm{T}}}). We then perform Id vs. Vds sweeps for each Lch at a common Vgs, recording the Vds at which the device with the ith channel length reaches Id = ({I}_{{rm{d}}}^{{rm{T}}}) as ({V}_{{rm{ds}}}={V}_{{rm{ds}}}^{(i)}) (Fig. 2b). Then, we plot ({V}_{{rm{ds}}}^{(i)}) vs. Lch and perform linear regression (Fig. 2c); the y-intercept of the line of best fit yields the voltage drop across the contacts ({Delta V}_{{rm{C}}}) at ({I}_{{rm{d}}}={I}_{{rm{d}}}^{{rm{T}}}). (ΔVC is the summed voltage drop across the source and drain contacts, not the average voltage drop across either contact.) Here, ({I}_{{rm{d}}}^{{rm{T}}}) must be chosen such that the extracted ({V}_{{rm{ds}}}^{(i)}) values are small (all ({V}_{{rm{ds}}}^{(i)}) ≪ Vgs − VT) to minimize the quadratic term in Eq. (1); otherwise, the linear fit in Fig. 2c becomes invalid. Additionally, a small ({V}_{{rm{ds}}}^{(i)}) ensures that the vertical electric field near the drain is similar for all channel lengths, helping to ensure that Rd remains constant across all devices.

Next, we partition ({Delta V}_{{rm{C}}}) into the voltage drops across the source and drain, ({Delta V}_{{rm{s}}}) and ({Delta V}_{{rm{d}}}). As Rs and Rd contain reverse- and forward-biased Schottky diodes, respectively, we have Rs > Rd20. Further, as Rd approaches 0 for high drain bias22, we have:

For simplicity, we take the centers of these ranges, i.e., ({Delta V}_{{rm{d}}}approx frac{1}{4}Delta {V}_{{rm{C}}}) and ({Delta V}_{{rm{s}}}approx frac{3}{4}Delta {V}_{{rm{C}}}), and estimate the true intrinsic voltages as ({V}_{{rm{ds}}}^{{prime} (i)}={V}_{{rm{ds}}}^{(i)}-{{Delta }}{V}_{{rm{C}}}) and ({V}_{{rm{gs}}}^{{prime} }={V}_{{rm{gs}}}-{{Delta }}{V}_{{rm{s}}}approx {V}_{{rm{gs}}}-frac{3}{4}Delta {V}_{{rm{C}}}).

We use the above approach to extract ({V}_{{rm{ds}}}^{{prime} (i)}) and ({V}_{{rm{gs}}}^{{prime} }) at multiple fixed Vgs values to compile the table in Fig. 2d. Next, we use these tabulated values to build a system of equations from which we extract μ and VT. To do so, we rearrange Eq. (1) into:

As Eq. (4) is in the form y = mx + b [with m = (2{V}_{{rm{T}}}), x = ({V}_{{rm{ds}}}^{{prime} }/{L}_{{rm{ch}}}), and b = (2{I}_{{rm{d}}}/(mu {C}_{{rm{ox}}}W))], we use rows from Fig. 2d to plot ((2{V}_{{rm{gs}}}^{{prime} }{V}_{{rm{ds}}}^{{prime} left(iright)}-{V}_{{rm{ds}}}^{{prime} left(iright)2})/{L}_{{rm{ch}}}^{(i)}) as a function of ({V}_{{rm{ds}}}^{{prime} (i)}/{L}_{{rm{ch}}}^{(i)}) and perform linear regression (Fig. 2e). We then use the extracted slope and intercept to calculate VT and μ from known quantities.

Although we present this derivation for n-type devices, this procedure can easily be adapted to p-type devices by repeating the derivation starting from the p-type analog of Eq. (1). Alternatively, one could apply the above procedure to p-type devices by negating the input Vgs, taking the absolute value of Vds, and then negating the extracted VT.

We note that (Delta {V}_{{rm{C}}}) extracted in Fig. 2c is accompanied by an associated error that leads to uncertainty in the extracted μ and VT. Simple analytic techniques cannot easily propagate this error to the final estimated μ and VT because the quantities along both the x- and y-axes in Fig. 2e are error-prone, where the errors in x and y values are not mutually independent. Hence, we instead use the Monte Carlo approach described in Supplementary Section 2 to propagate this error, allowing us to improve the estimates for the nominal μ and VT and their standard errors. This Monte Carlo approach is implemented in Python code that we provide in Supplementary Section 4 and in an online GitHub Repository19.

Model validation

We validate our proposed extraction by using it to estimate μ and VT from current-voltage characteristics generated by Sentaurus Device TCAD18. This approach allows us to assess the accuracy of the extraction because μ and VT are known a priori: μ is a simulation input parameter, and the channel VT can be extracted from equivalent devices (simulated in Sentaurus) without contact resistance.

The contact-gated devices in our TCAD simulations have nominal Schottky barrier heights ϕB = 0.15, 0.3, 0.45, and 0.6 eV. These are “nominal” values because the TCAD simulations include image force lowering (IFL)23 and tunneling at the contacts; these listed ϕB are barrier heights before IFL (i.e., the ϕB we list are the differences between the semiconductor’s electron affinity and the metal’s work function). All devices are back-gated transistors (Fig. 1a) with HfO2 gate insulators (relative dielectric constant κ = 20 and equivalent oxide thickness EOT = 10 nm). The channel thickness is 0.615 nm (corresponding to monolayer MoS224,25) and the mobility is set to μ = 50 cm2V-1s-1.

In Fig. 3a–d, we plot TCAD-generated Id vs. Vov sweeps (where the overdrive voltage Vov = Vgs − VT) at Vds = 0.1 V for each ϕB at Lch = 200, 400, …, 1000 nm. Devices with ϕB ≥ 0.3 eV clearly display the signature kink of contact gating7 (especially at small Lch, where RC exceeds the channel resistance at low Vov). Next, we plot the extracted μ and VT for each ϕB using our proposed extraction method and three conventional techniques: the linear extrapolation, Y-function, and TLM approaches1,16,26. These conventional techniques are applied directly on the synthetic Id vs. Vgs data shown in Fig. 3a–d, whereas our extraction uses separate synthetic Id vs. Vds data. The linear extrapolation and Y-function techniques both use the device with the longest channel (Lch = 1000 nm), whereas our proposed method and the TLM approach use the full range of Lch = 200–1000 nm in Fig. 3a–d. We calculate standard error using the method described in Supplementary Section 2 for our proposed extraction method, and we use the standard error from linear regression (equivalent to the 68% confidence interval) for the TLM approach. (We do not include standard error for the linear extrapolation or Y-function approaches because the synthetic data is noiseless.)

Id vs. Vov for families of devices with Lch = 200, 400, …, 1000 nm and Schottky barrier height ϕB = a 0.15 eV, b 0.3 eV, c 0.45 eV, and d 0.6 eV. x-axes show different ranges of Vov/EOT to highlight device characteristics and extractions near Id turn-on for different ϕB. Solid gray lines mark the approximate Id turn-on for each device family. e The mobility μ extracted with our method and the linear extrapolation, Y-function, and TLM approaches for device families with ϕB = 0.15 eV, f 0.3 eV, g 0.45 eV, and h 0.6 eV plotted vs. Vov/EOT. Horizontal dashed lines mark the true μ. The x-axes are the same as in i–l. i The threshold voltage VT extracted with each method for device families with ϕB = 0.15 eV, j 0.3 eV, k 0.45 eV, and l 0.6 eV plotted vs. Vov/EOT. The horizontal dashed lines mark the true channel VT.

In Fig. 3e–h, we plot the μ extracted from each method vs. Vov/EOT. The horizontal axes in these plots are shown only up to the point where the μ obtained by the four extraction methods have converged. At ϕB = 0.15 eV (Fig. 3e), we find that all extractions yield reasonable estimates for μ, with a worst-case underestimation of ~15% for the Y-function method. As ϕB increases, however, we find that conventional methods begin to severely overestimate μ due to contact gating. We also note the TLM approach predicts a small standard error (<10%) in Fig. 3g, h (ϕB = 0.45 and 0.6 eV) despite overestimating μ by over 2×. In other words, the standard error estimated from the TLM approach does not accurately reflect the true uncertainty in the extracted μ when ϕB is large and Vov is limited (e.g., by early dielectric breakdown). In contrast, our method estimates μ more accurately than conventional methods, with a worst-case overestimation of ~20% at ϕB = 0.6 eV and low Vov (Fig. 3h), and with the true μ being captured within our error bars (unlike the TLM method).

We note that the TLM approach requires that devices with different Lch be measured at a common carrier density, i.e., at a common Vov1. In the present work, Vov is referenced with respect to the VT estimated by linear extrapolation; in Supplementary Section 3, we study the accuracy of the TLM approach when instead using VT defined at a constant current (e.g., 100 nA/μm).

Next, in Fig. 3i–l, we plot the VT extracted from our proposed method, the linear extrapolation method, and the Y-function method vs. Vov/EOT using the same horizontal x-axis limits as in Fig. 3e–h. Importantly, in these transistors, contact gating obscures the channel turn-on, causing the linear extrapolation and Y-function methods to significantly overestimate VT. In comparison, we find that our proposed extraction tends to yield much more accurate VT estimates, with a worst-case VT error of 0.2 V in the range of Vov/EOT plotted in Fig. 3i–l. We note that our method and the conventional methods tested here do not always converge to the true VT at higher Vov, but this is acceptable because the error in estimated VT is less impactful (i.e., has smaller impact on the predicted charge carrier density) at large Vov.

To ensure that our proposed extraction is applicable to a variety of devices (and not limited to those presented in Fig. 3), we repeat similar extractions for back-gated transistors with (i) μ = 5 cm2 V−1 s−1 and EOT = 10 nm and (ii) μ = 50 cm2 V−1 s−1 and EOT = 100 nm (channel thickness = 0.615 nm and ϕB = 0.45 eV for all devices) in Fig. 4. These scenarios are relevant because they correspond to typical devices used to test emerging semiconductor channels. We plot Id vs. Vov in Fig. 4a, b, extracted μ in Fig. 4c, d, and extracted VT in Fig. 4e, f. We find that the trends observed here are similar to those of Fig. 3, suggesting that our proposed extraction remains applicable at higher EOTs or lower μ. Thus, the method we propose in this work appears to facilitate accurate extractions from a variety of contact-gated transistors with high RC and/or early dielectric breakdown that cannot access the higher Vov range necessitated by conventional methods.

Id vs. Vov for families of devices with Lch = 200, 400, …, 1000 nm and Schottky barrier height ϕB = 0.45 eV with a EOT = 10 nm and mobility μ = 5 cm2 V−1 s−1 and b EOT = 100 nm and μ = 50 cm2 V−1 s−1. The solid gray lines mark the approximate Id turn-on for each family of devices, and the x-axes are the same as in c, d and e, f. c The extracted mobility μ with our method and the linear extrapolation (LE), Y-function (Y), and TLM approaches for device families with EOT = 10 nm and mobility μ = 5 cm2 V−1 s−1 and d EOT = 100 nm and μ = 50 cm2 V−1 s−1 plotted vs. Vov/EOT. The horizontal dashed line marks the true μ. e The threshold voltage VT extracted with each method for devices with EOT = 10 nm and μ = 5 cm2 V−1 s−1 and f EOT = 100 nm and μ = 50 cm2 V−1 s−1. Horizontal dashed lines mark the true channel VT.

Effect of device-to-device variation

To assess the robustness of our extraction, we apply it to devices whose μ and VT have a certain amount of variation, as would be seen experimentally. For each device, we randomly select μ and VT according to Gaussian distributions with means (standard deviations) of 50 cm2 V−1 s−1 (10%) and 0.56 V (0.1 V), respectively. As before, we use Sentaurus TCAD18 to generate current-voltage characteristics that we analyze with our proposed method and the TLM approach. Because the Y-function and linear extrapolation methods are applied to one device at a time, they are not affected by variations between devices; thus, we do not re-analyze them here. We quantify each method’s accuracy in terms of its mean absolute error (MAE) and its confidence interval coverage probability (CICP; the probability that the true μ lies within the range of estimated value ± the error). In other words, an MAE near 0% (or as small as possible) and a CICP close to 100% (or as large as possible) are desirable. All devices are identical to those used in Fig. 3c, i.e., back-gated with EOT = 10 nm, channel thickness = 0.615 nm, and ϕB = 0.45 eV.

We perform 100 extractions on families of devices with 5 channel lengths (Lch = 200, 400, …, 1000 nm), starting at high Vov/EOT = 0.64 V/nm. We find that our proposed approach and the TLM approach offer reasonably small MAE = 14.3% and 10.9% (on the same order as the μ standard deviation), respectively, and CICPs of 99% and 65%, respectively (Fig. 5a, b), indicating that random variation does not significantly affect the accuracy or reliability of these methods at high Vov.

Histograms of mobility overestimations for 100 families of devices with Lch = 200, 400, …, 1000 nm. The devices are selected at random from a Gaussian distribution with mean (standard deviation) μ = 50 cm2 V−1 s−1 (10%) and mean (standard deviation) VT = 0.56 V (0.1 V). a Our method and b the TLM approach at high Vov/EOT = 0.64 V/nm. c Our method and d the TLM approach at lower Vov/EOT = 0.3 V/nm. e Our method and f the TLM approach at Vov/EOT = 0.3 V/nm with three of each Lch used in the extraction. Each figure lists the mean absolute error (MAE, ideally should be close to 0%) and confidence interval coverage probability (CICP, ideally should be close to 100%).

Next, we repeat this procedure at smaller Vov/EOT = 0.3 V/nm, which lies within the contact-influenced region of the Id vs. Vov curves in Fig. 3c. Here, the MAE of our proposed method increases to 20.2% and its CICP remains high at 94% (Fig. 5c). However, the MAE of the TLM approach increases greatly to 116.0% (>2× mobility overestimation), whereas its CICP falls to 0%, i.e., the TLM approach did not estimate μ to within error bars across any of the 100 trials (Fig. 5d). The MAE of our approach can be improved by adding more devices; repeating the extraction at Vov/EOT = 0.3 V/nm using three of each Lch (Fig. 5e; with devices subject to the same random variations as before) decreases the MAE of our approach to 13.3%, though the CICP also worsens slightly to 78% (which may occur in part because the estimated standard error shrinks). However, the MAE of the TLM approach only decreases slightly to 110.0% (~2× mobility overestimation) and the CICP remains at 0% (Fig. 5f), indicating that adding more devices to the TLM analysis is ineffective for improving both accuracy and reliability at Vov/EOT = 0.3 V/nm.

We note that although Fig. 5c shows our method yields a reasonably low MAE = 20.2% on the entire set of 100 device families, the 10 worst extractions still overestimate μ by 48% to 102%. However, the CICP considering only these 10 extractions is 100%, i.e., each of these 10 worst extractions also yielded large estimated errors that encompassed the true μ of 50 cm2 V−1 s−1. Thus, although our method can overestimate μ of contact-gated devices (here with ϕB = 0.45 eV), these overestimations are accompanied by large error bars that clearly indicate when the extraction is error-prone.

Discussion

We have developed a simple method for extracting the mobility and channel threshold voltage from transistors with gate-voltage-dependent contact resistance. We tested this method by analyzing TCAD-generated current-voltage characteristics and showed it can accurately extract the mobility and threshold voltage when devices are heavily influenced by contact gating, even when conventional methods overestimate the mobility by 2–3×. We also find that the standard error associated with the estimated mobility and threshold voltage tends to accurately reflect the actual uncertainty in the extraction, enabling a high confidence extraction of mobility even in regimes where the TLM approach fails. Hence, our method expands the range of overdrive voltages that can be used to estimate mobility and threshold voltage, allowing these quantities to be more accurately determined in emerging semiconductor devices with high contact resistance and/or early dielectric breakdown.

Responses