Solution-processable 2D materials for monolithic 3D memory-sensing-computing platforms: opportunities and challenges

Introduction

Silicon CMOS microchip has been the cornerstone of microelectronics for several decades, enabling remarkable progress in computing and memory technology. In the past decades, the ongoing trend of scaling down device dimensions has significantly propelled advances in key metrics (power, performance, area and cost reduction) of silicon technology1. These advancements have led to various technological revolutions, including the rise of Artificial Intelligence, the Internet of Things and Big Data, and thus have brought forth new demands for data collection (sensors), processing (computing unit), and storage (memory) in the future energy-efficient and data-centric electronic system. However, silicon-based CMOS devices are encountering insurmountable challenges due to limitations in miniaturization and escalating complexities in manufacturing processes. The traditional separation of memory and logic units in the von Neumann computing paradigm has also created bottlenecks in energy efficiency, prompting a shift towards in-memory and near-memory computing models2,3. In addition, with the exponential growth of sensory nodes4, it becomes imperative to not only explore cost-effective and practical methods for integrating new materials on silicon CMOS wafers, but also to innovate novel mechanisms and architectures capable of efficiently processing unstructured and redundant sensory data within this evolving computing paradigm.

In this context, M3D integration, as illustrated in Fig. 1, where sensors, memories, and transistors are incorporated sequentially above silicon CMOS logic between layers of fine-grained and dense vertical interconnects, holds significant potential as a key enabler for system-on-chip hyperscaling5,6. By stacking and connecting the memory, computing, and sensor units closer through dense vertical interconnections (vias), the data communication bandwidth is greatly improved, and thus latencies associated with data exchange bottleneck between compute and memory can be substantially reduced, enabling efficient on-chip data-abundant processing. Despite the promising nature of such 3D systems, there are fundamental obstacles that must be overcome. One major roadblock is the incompatibility between the thermal budget of the transistors and interconnects. Advanced low resistivity copper interconnects with low-(kappa) dielectric interlayers are unable to withstand thermal exposure above 400 °C. However, the thermal activation of dopants in silicon-based devices typically occurs between 600 and 1000 °C. Therefore, processing silicon transistors below such temperatures results in performance and reliability degradations.

An overall graphic illustration of M3D integration of memory, sensing, and computing devices with solution processable 2D materials. This provides a comprehensive visual representation of the key components and concepts central to the discussion in this review.

The current dilemmas with silicon material for massive 3D systems have motivated persistent efforts in the search for beyond silicon materials solution. Among them, 2DMs, a broad class of nanomaterials, offer a myriad of opportunities to tailor the electronic properties with desired mobility, bandgap, and carrier concentration, essential for the realization of highly efficient M3D circuits5,7,8,9. On one hand, the atomically thin nature of 2DMs can help mitigate short-channel effects, such as drain-induced barrier lowering (DIBL), which is crucial for scaling transistors below 3 nm technology nodes10. On the other hand, 2DMs can be integrated with low-thermal budget processing, making it a compelling technology for M3D integration compatible with thermal process constrained interconnects (e.g. low-(kappa) dielectric and copper interconnects). Furthermore, 2DMs encompass a wide variety of electronic building blocks ranging from semiconductors11,12,13, insulators14,15,16, ferroelectrics17,18,19,20, magnets21,22,23, to topological insulators24,25,26. This diverse range of properties and functionalities provided by 2DMs offer flexible designs of innovative memory, sensing and computing devices and a unique platform for the rapid design and implementation/verification of M3D circuits. Moreover, the weak van der Waals (vdW) interlayer bonding, diverse electronic properties and wide range of vacancy dynamics associated with 2DMs and vdW heterostructures offer a new palette to engineer their defects, composition, and even stacking sequences for monolithic integration of devices with different functionalities, such as storage, computation, and sensing, on a single chip27. Especially, the high surface-to-volume ratio and versatile functionalization make 2DMs well-suited for gas, chemical, and biosensing applications. Therefore, the fusion of various 2DMs functional devices through M3D integration can lead to compact and multifunctional integrated circuits with enhanced system performance and area efficiency beyond the conventional von Neumann architecture.

So far, deposition and transfer of 2DMs are active areas of research and development, with promising progress28,29,30. However, they have not yet reached full manufacturability and the current approaches to wafer-level, defect-free, single-crystalline growth and transfer still present fundamental challenges. As such, the feasibility of such approaches for seamless integration with silicon CMOS technology and final translation into future M3D circuits is still in question. Such co-integration technology has to overcome hurdles from key ‘unit process’ for wafer-level scalability, reliable high-throughput thin-film transfer processes and CMOS-compatible integration techniques31. In contrast, solution-processable 2DMs not limited by wafer-scale transfer process, offer an interim and alternate integration option. Solution-processable 2DMs refer to a distinct class of 2D nanosheets that exhibit the ability to disperse in various solvents, allowing for facile processing and manipulation like organic materials32. The solution processability of these 2DMs nanosheets enables them to be deposited onto various substrates or the fabrication of thin films through scalable and cost-effective liquid-based techniques such as spin-coating33,34, drop-casting35, printing36,37,38, self-assembling39,40,41, etc. Despite their solution-based processability, they retain the excellent electronic performance and structural stability of crystalline inorganic materials, making them attractive for a wide range of applications in electronics, optoelectronics, energy storage and sensing5,32,33,42,43,44,45,46,47. Furthermore, with low process temperature and compatibility with high-precision optical lithography patterning, solution-processed 2DMs offer a practical approach for the M3D integration of tall and flexible 2DMs stacking that circumvents the challenges faced by chemical vapor deposition (CVD) synthesis and mechanical transfer process.

In view of the many advantages that solution-processable 2DMs bring for the next generation of monolithic 3D electronics, we aim to present a comprehensive review that covers recent advances, open challenges and future perspectives of solution-processable 2DMs-based devices, ultimately steering towards the convergence of memory, sensing, and computing functionalities. The overview of this review is encapsulated in Fig. 1, highlighting four key aspects. First, from the perspective of material science, we review the past decade of progress in exfoliation chemistry, deposition techniques and post-processing treatments. This initial section elucidates how various advancements in this domain enabled the development of electronic grade 2D nanosheets and films for different devices applications. Building upon this foundation, we transition seamlessly into device applications. This section explores the performance limitations and breakthroughs of solution-processable 2DM-based transistors, memristors and photodetectors. To optimize device performance for future sensing-memory-computing systems, the third section offers a detailed review of the fundamental charge transport mechanisms in solution-processed 2DMs devices. Additionally, we delve into the critical process parameters for the heterogeneous integration of 2DMs-based memory, sensing, and computing functionalities, as well as novel computing systems and architectures. Lastly, we summarize the challenges and potential synergies emerging from the logic-memory-sensing convergence, culminating in a comprehensive outlook that addresses the hurdles and prospects on the horizon for solution-processable 2DM-based electronics.

Materials synthesis and deposition

Exfoliation and formulation of 2D dispersions

The reliable generation of well-dispersed 2D nanosheets in a solution with long-term stability and nanosheet size/thickness homogeneity is essential for the subsequent assembly of thin films formed from a network of 2D nanosheets. These nanosheets need to exhibit a range of interesting flake-size dependent electronic properties to enable diverse nanomaterial functionalities as a thin film composite, including metallic (e.g., graphene48,49,50), semiconducting (e.g., transition metal dichalcogenides, TMDCs38,41,51 and black phosphorus, BP52,53,54), and insulating (e.g., hexagonal boron nitride, h-BN15,50,55) characteristics. Generally, there are two approaches to producing 2D nanosheet dispersions: the bottom-up synthesis34,56,57,58 and the top-down exfoliation strategies59,60. The former usually involves a highly specific colloidal chemistry process and undesired surface ligands, leading to 2D nanosheets with poorly controlled chemical composition, broad width/thickness distribution and compromised electrical properties (e.g. conductivity and mobility), thus rarely used for electronic purposes. Instead, top-down exfoliation approaches, which utilize either direct liquid-phase exfoliation (LPE) or intercalation-assisted exfoliation technique as shown in Fig. 2a-c, have demonstrated to be more effective for producing graphene61,62, h-BN54,55, 2D TMDCs63,64,65, BP66,67, etc. Because of their anisotropic bonding (covalent within the layer and van der Waals interactions between layers), external forces such as high-power sonication or high-shear mixing typically involved in the direct LPE process can be utilized to overcome the weak interlayer interactions in 2D bulk crystals and facilitate the isolation of mono- to few-layer nanosheets. Despite a straightforward and general approach, direct LPE usually suffers from long-term agitation, poor exfoliation yield ((< 40 %)) as well as small nanosheet size (<1 µm)44. Furthermore, the use of organic solvents with high-boiling points, such as N-methyl-2-pyrrolidone or dimethylformamide, introduces surface contamination68.

a Direct LPE. b Electrochemical exfoliation with the assist of large molecules intercalation. c Electrochemical exfoliation with the assist of small ions intercalation. Comparison of direct LPE and electrochemical exfoliation in terms of (d) thickness and lateral dimension of exfoliated nanosheets, and (e) exfoliation yield as a function of exfoliation duration. f Example of MoTe2 flake size distribution produced from intercalation with large molecules. Panel f reprinted with permission from ref. 238, American Chemical Society.

Recently, intercalation-assisted exfoliation technique (also called electrochemical exfoliation technique) has been developed to enhance the exfoliation yield by inserting either small-sized alkali metals or large-sized organic ammonium cations between the vdW interlayers prior to exfoliation63,64,65,67,69,70,71,72. The intercalation process increases interlayer spacing without breaking intra-layer covalent bonds, significantly weakening the interlayer bonding, thus facilitating the subsequent delamination steps. Compared to direct LPE, intercalation-assisted exfoliation allows the production of high-quality 2D nanosheets with significant improvement in average aspect ratio and less exfoliation duration (Fig. 2d, e)73. Intercalation with alkali metal ions like Li+ and Na+ has been demonstrated to be a viable method for selectively producing pure mono- or few-layer TMDC nanosheets. For instance, monolayer MoS2 nanosheets were achieved with a yield of 92%74, monolayer TaS2 nanosheets with a yield of 93%75 and bilayer TiS2 nanosheets with a yield of 93%76, all exhibiting lateral dimensions in the micrometer scale. However, the fast and spontaneous lithiation process can introduce many defects77 or cause semiconducting to metallic phase transition (e.g., semiconducting 2H to metallic 1 T/T’ phase transition in MoS2) due to the excessive injection of electrons78.

Replacing the small Li+ ions with large organic ammonium cations, such as quaternary ammonium ions, allows for a milder reaction and mitigated electron doping, resulting in few-layered semiconducting nanosheets with desired phase and minimum structural damage32,65,66. For example, phase-pure, semiconducting 2H-MoS2 nanosheets have been achieved by the insertion of organic quaternary ammonium molecules, which enables a tremendous increase in interlayer spacing of host MoS2 crystal from the original 6.1 Å to 22.9 Å65. Yu et al. optimized the electrochemical intercalation method with the assistance of polyvinylpyrrolidone, which enables the high-yield (>95%) exfoliation of micron-sized (5-10 µm), monolayer MoTe2 nanosheets (Fig. 2f). It is important to note that intercalation-assisted exfoliation is a complex process that depends on several factors, including the intercalant size and chemistry, interlayer spacing, inherent intralayer bond strength, intercalation conditions, etc. The effect of molecule size on the geometric dimensions of 2D nanosheets has been investigated by comparing the intercalation with tetrapropylammonium (TPA, molecule size d (approx) 10 Å) and tetraheptylammonium (THA, molecule size d (approx) 20 Å) in the exfoliation of ReS2 flakes, respectively63. A critical molecular size effect was found, where the larger-sized THA exhibited improved efficiency in producing thinner and bigger ReS2 nanosheets with an increased density of grain boundaries. However, there is a tradeoff between the intercalant size and diffusion kinetics. On one hand, the increase in the intercalant size causes dramatic interlayer expansion, which could weaken the interlayer bonding beneficial for the delamination of bulk crystals. On the other hand, it increases the intercalation barrier through a notorious self-retarding effect64, where the presence of large-size ammonium cations already intercalated within the vdW gaps creates significant elastic and electrostatic interlayer repulsions, preventing complete intercalation in every vdW gap79,80,81.

Several strategies have been reported to address the self-retarding issues or high diffusion barriers. A co-intercalation of organic ammonium cations solvated with neutral solvent molecules is reported as an efficient strategy for sufficient intercalation of bulk crystal and notably reduces the excessive charging and structural damage of the layered hosts36. With such strategy, a wide range of superconducting 2D monolayers (e.g. NbSe2, NbTe2, TaS2, TaSe2, TiS2, TiSe2 and MoTe2) have been produced with lateral dimensions up to 300 µm36. In addition, the self-refreshing process through intercalation-induced strain is another solution to self-retarding effect64. But such a strategy only applies to certain 2D materials with high rigidity such as In2Se382, InSe and Bi2Se364, which experience intense mechanical strain during intercalation, leading to a sequential process of bending, fracture, and detachment from the bulk crystals. As a result, underlying fresh surfaces are continually exposed for intercalation and thus effectively avoid the self-retarding effect.

Assembly and deposition of 2D film

The scalable assembly of liquid-exfoliated 2D nanosheets into continuous and large-area thin films represents a crucial step towards their implementation in solid-state electronic devices for memory, sensing, and computing applications. To this end, a plethora of techniques, such as spin coating33,34,65, inkjet printing49,50,83,84,85, aerosol jet printing38, Langmuir-Blodgett assembly41,86,87 and electrostatic deposition39, each with its distinct advantages and disadvantages, have been developed for the scalable assembly of composite thin film from solution-processed 2D nanosheets. The appropriate deposition technique should be selected to form the desired thin film structures based on the material’s properties and target applications. In this review, we will specifically delve into the most widely adopted methods, namely spin coating, inkjet printing, and Langmuir-Blodgett assembly (Fig. 3a-c). As a versatile technique, inkjet printing is a promising approach because of its precise control over the deposition process, high resolution (~50 µm) and low material losses ( < 1 mL)88. During the printing process, the droplets containing the 2D nanosheets dispersions are ejected from the micro-sized nozzles onto target substrate in a highly controlled and precise manner, creating complex patterns and intricate designs. Unlike traditional lithography techniques, inkjet printing enables on-demand deposition of 2D nanosheets onto any substrates in a maskless and non-contact deposition mode, thus suitable for large-scale, flexible and wearable electronics. Various electronics have been demonstrated by inkjet printing different 2D materials inks ranging from graphene89 to TMDCs37,51,90,91,92,93, BP53, etc. A comprehensive engineering of ink properties (e.g. surface tension, viscosity, boiling point, and concentration) must be performed to realize stable 2D inks and ensure satellite droplet-free ejection, high throughput, as well as uniformly printed films85.

Film deposition techniques for 2D dispersions and their corresponding nanosheets alignment morphology. a Printed film with oblique alignments. b Spin coated film with plane-to-plane alignment. c Langmuir-Blodgett assembled film with edge-to-edge alignment. Scalebars in b and c are 10 nm and 2 µm, respectively. Post processing treatment of the solution-processed film. d Chemical treatment. e Thermal annealing. f Laser thinning. Panel a reprinted with permission from ref. 33., Springer Nature Limited; Panel b reprinted from ref. 50., Springer Nature Limited; Panel c reprinted from ref. 40., American Chemical Society.

Despite their huge potential, the printed electronic devices reported to date are still challenged by poor performance and large device-to-device variation inferior to those made from exfoliated flakes or CVD film. This discrepancy comes from the morphology of the printed film, or more specifically, the alignment of the nanosheets. Figure 3a presents a scanning electron microscope image of the channel region from an inkjet-printed h-BN/graphene heterostructure transistor, where randomly aligned nanosheets with poor interface and pinholes are clearly seen in the vertical vdW stacks50. In such a system, charge transfer across the inter-sheet junction experiences high parasitic resistance that ultimately deteriorates their film mobility. As a result, the film mobility from the printed nanosheets generally falls within a narrow range between 0.01 ~ 1 cm2V−1s−1, almost two orders of magnitude lower than the mobility of mechanical exfoliated TMDCs (~50 cm2V−1s−1)90, MXenes (~100 cm2V−1s−1)94 and graphene nanosheets ( > 10,000 cm2V−1s−1)95, respectively. This highlights the fundamental role that inter-sheet junctions play in moderating the network properties, which will be illustrated in greater detail in Section “Physical insights into the charge transport mechanism in solution processable transistors, RRAM and sensors”. An intriguing exception to the reduced mobility has been reported for the MoS2 semiconducting film and Bi2Se3 conductive film produced by spin-coating. Remarkably high thin-film mobility of approximately 10 cm2V−1s−1 for MoS265 and 113 cm2V−1s−1 for Bi2Se334 are achieved, respectively, which are even comparable to their individual nanosheets. This exceptional performance can be attributed to the nanosheets’ inherent flexibility and reduced grain boundaries associated with thin and large nanosheet geometry, leading to a favorable large-area plane-to-plane alignment (Fig. 3b). Consequently, a significant reduction in junction resistance occurs, effectively shifting the rate-limiting factor to the intrinsic resistance of the nanosheets. Therefore, spin-coating has been widely employed for depositing 2D nanosheets onto different substrates, offering simplicity and capability for producing high-quality and uniform thin films. However, achieving full coverage on a substrate often demands high nanosheet concentration (e.g., 10 mg/mL) during spin-coating iterations65, which will not only cause substantial materials waste and stability concern of the 2D dispersions, but also impose challenges for precise control over film thickness and architecture, resulting in irregular structure of agglomerated nanosheets after the solvent evaporates.

Alternatively, given exceptional versatility and capability of microstructural control, the Langmuir–Blodgett (LB) assembly approach is becoming increasingly popular for the deposition of large-area thin film with superior 2D nanosheet alignment and uniform thickness (Fig. 3c)39,87,96,97,98. It offers precise control over nanosheet density and relative orientations within a monolayer, capable of fabricating well-defined thin film structures with customized number of layers. In a typical LB assembly procedure, the 2D nanosheets are initially dispersed in a volatile water-immiscible organic solvent, followed by spreading onto the water surface. After the spreading solvent evaporates, a monolayer consisting of 2DM flakes forms on the water, which is subsequently transferred to the target substrate, eventually creating a large area of flat 2D thin film. Through LB assembly at the air/liquid interface, monolayers of diverse colloidal 2DMs have been widely demonstrated so far39,40,87,98,99,100. However, there are some concerns associated with air/liquid confinement in LB assembly. One issue is the material loss to the water subphase during the transfer process, leading to the reduction in monolayer quality and yield. Furthermore, the compression of particles at the air/liquid interface may lead to aggregation, compromising the uniformity of the assembled monolayer. As a result, liquid/liquid confinement techniques have been further utilized to enhance the alignment of nanosheets86,98. The choice of solvents for interfacial confinement in LB assembly plays a crucial role in determining the film quality, structure, and functionality. Different solvents possess varying polarities, surface tensions, and viscosities, which in turn influence the assembly process and the packing of the molecules or nanoflakes in the resulting LB films. For example, a monolayer of ultrathin sheets of highly hydrophobic graphene nanosheets was assembled at the chloroform/water interface86. Driven by the minimization of interfacial energy, the graphene nanosheets spatially confined at the immiscible liquid/liquid interface produce a closely packed monolayer structure with excellent electrical conductivity (1000 S/cm) and optical transmission (>70% @ 550 nm). In the case of MoS2, the water/hexane system, characterized by its high interfacial tension (~50.5 mN/m), was deliberately selected to create the interface, leading to the self-assembled tiling of MoS2 bilayer nanosheets with edge-to-edge contacts between nanoflakes (Fig. 3c). Remarkably, over 70% of the film is covered by single flakes without overlapping, showcasing the efficacy of this solvent-driven approach in achieving highly organized and non-overlapping thin films. However, scaling up the LB assembly process to produce films over a wafer scale with consistent quality can be very challenging, which needs delicate control over the interfacial conditions and solvent interactions to promote the desired arrangement of the materials. Overall, maintaining a stable interface during the assembly process, achieving well-spread nanosheets with minimal aggregation at the interface, and ensuring a steady and controlled film transfer process are the three most important considerations for successful LB film fabrication.

Post treatment of 2D film

Low interface quality and abundant defect density or dangling bonds at the flake junction regions largely compromise the electronic properties of solution-processed 2D film due to the charge trapping of carriers. Therefore, enhancing the quality of nanosheet films and mitigating defects through post-treatments such as thermal annealing, chemical modifications (e.g. bis(trifluoromethane) sulfonimide101 or conjugated 1,4-benzenedithiol treatments) and laser thinning presents a promising pathway for high-performance electronics (Fig. 3d–f). These strategies hold significant potential for optimizing the electronic properties of nanosheet-based materials.

Thermal annealing stands out as the primary post-processing technique, widely employed to eliminate volatile components and polymeric additives within the nanosheet film. In some cases, certain polymers can promote nanosheet doping49,102, but their presence within a network typically creates physical barriers between nanosheets. The elimination of polymers brings about several benefits. Firstly, it triggers a collapse in the network structure89, leading to reduced porosity. This structural transformation facilitates closer contact between nanosheets. Furthermore, the resulting carbonization leaves behind a residue that might enhance inter-sheet charge transfer under specific conditions103. The conductivity of the nanosheets film is highly correlated to the annealing temperature. Annealing temperature higher than 250 °C is usually required to fully remove the polymer and maximize the conductivity. Besides, the annealing temperature may vary depending on the types of polymers. For instance, Secor et al. 104. systematically studied the electrical conductivity of graphene networks as a function of annealing conditions. They found that annealing at 250 °C for 20 minutes effectively removed the polymeric binder ethyl cellulose, achieving a maximum conductivity of 2.5 × 104 S/m. In the case of polyvinylpyrrolidone, He et al. 105. reported that annealing between 300-350 °C is necessary to convert polyvinylpyrrolidone into a thin layer of amorphous carbon, resulting in π-π stacking that bridges graphene flakes. This significantly enhances the conductivity of the network, reaching 8.8 × 104 S/m. However, it is important to note that the thermal stability of nanosheet materials can impose limitations on the annealing temperature. For instance, TMDCs, like WSe2 are very vulnerable to oxygen and moisture. Annealing those chalcogenides at temperatures exceeding 200 °C in an oxygen-rich environment can trigger undesired p-type doping106. Moreover, temperature beyond 300 °C might induce considerable oxidation, converting the material to oxides106,107. The thermal budget places constraints on annealing temperatures, necessitating the adoption of additional protective measures such as vacuum or inert gas environments. This is crucial to prevent degradation of material quality and enhance the conductivity of the networks.

Complementary to thermal annealing, chemical treatments serve as another valuable tool for enhancing the properties of solution-processable 2D nanosheet films (Fig. 3d). Generally, the energetic liquid exfoliation procedure often introduces abundant structural defects like chalcogen vacancies in TMDCs. Those defects, unfortunately, can hamper the potential of these materials, especially in applications related to optoelectronics. Moreover, certain 2D materials, such as BP, are intrinsically unstable during solution processing, posing limitations for their practical use under ambient conditions. In the face of these challenges, the significance of chemical treatment becomes even more pronounced. To address structural defects in TMDCs, thiol molecules with various functional groups like bis(trifluoromethane)sulfonimide have been employed to tightly bond with sulphur vacancies and achieve controlled doping in TMDCs through charge transfer34,101,108. This molecule engineering approach has been applied to establish covalent bonds between neighbouring nanosheets in MoS2 networks with aromatic and conjugated 1,4-benzene-dithiol molecules109. This innovative strategy ameliorates sulphur vacancies and forms covalent bridges between adjacent nanosheets, facilitating percolation pathways for efficient charge transport. To address the materials stability challenges, covalent functionalization with diverse reactive intermediates such as free radicals110, nitrenes111, carbocations112, and formation of molecular heterostructures82 has been successfully demonstrated to improve the environmental stability of BP nanosheets. Those molecules establish a strong interfacial coupling with BP nanosheets and induce substantial charge transfer that diminishes surface electron density and protects BP nanosheets from oxidation. This significantly prolongs their durability in ambient conditions. These examples underscore the critical importance of chemical treatment in tailoring the properties of solution-processed 2D films. By leveraging molecular interactions through chemical treatment, researchers have been able to mitigate structural defects, enhance stability, and improve charge transport properties, essential for realizing high-performance devices.

Given the nanosheets network morphology and intrinsic variability in nanosheet size and thickness, solution-processed 2D films are relatively thick with inherent uneven surface. This significantly impedes their application areas and raises device reliability concern, such as in transistors, where thin channels are preferred for better gate control and reduced short-channel effects in scaled devices. Therefore, efficient thinning techniques with precise layer control in a self-limited manner are crucial to address the thickness and uniformity issues associated with solution-processed 2D films (Fig. 3f). To date, high-energy lasers113,114,115, focused-ion beams116,117, gaseous-phase treatments118, and plasma-based etching119,120 have been developed to control the layer and patterning of 2DMs. Focused-ion beams and high-energy lasers have shown to be effective for controlled etching of MoS2114, BP115, graphene121, and others. Specifically, in TMDCs like MoS2, the strong thermal coupling of the bottom-most layer to the substrate allows for thinning in an atomic layer-by-layer manner through heating with continuous wave lasers114. The laser sublimates the uppermost layers through thermal absorption, while the strong thermal coupling of the bottom-most layers with the substrate prevents excessive thinning. For instance, Bissett et al. 122 demonstrated successful thinning of WS2 flakes from multilayer to monolayer using a laser power of ~20 mW (power density ∼2.45 MW/cm2) with an exposure time of 100 ms per step, resulting in an eightfold increase in photoluminescence intensity. Castellanos-Gomez et al. 114 further demonstrated on-demand fabrication of MoS2 monolayers by modulating the power of a 514 nm laser. When the laser power was between 10 and 17 mW, multilayer MoS2 was thinned down to monolayers. Power levels above 17 mW resulted in cutting through the layers, while power below 10 mW had no effect. At an optimal rastering rate of 8 µm2/min, laser thinning shows promise for small-scale and precise production of single-layer MoS2 structures. However, its overall throughput remains limited, posing challenges for large-scale manufacturing. Through cyclical steps of self-limited oxidation and selective etching, Nipane et al. 118 demonstrated a wafer-scale and selective atomic layer etching technique on mechanical exfoliated WSe2 flakes. In a typical process, the topmost WSe2 layer was oxidized in ozone under UV light exposure for 30 minutes at room temperature. Subsequently, the oxidized layer was removed by KOH etching (1 M, 10 seconds), followed by a rinse with deionized water. Such technique provides a precise and controlled means to thinning and flattening the rough surfaces of solution-processed 2D films.

Overall, advances in post-deposition processes are critical for expanding the application of 2D films in electronics, such as sensing, memory, and computing. Post-treatments like thermal annealing, chemical treatment, and laser thinning can significantly improve film quality by addressing issues such as inter-flake contact123, defect density109, and thickness control113,114. However, challenges inherent to deposition methods, such as random nanosheet alignment in solution-based techniques, remain difficult to overcome. While post-treatments can enhance inter-nanosheet contact123, they cannot fully correct misalignment, which fundamentally limits electronic performance. Langmuir-Blodgett assembly offers better control over nanosheet alignment40, yielding more uniform films, but faces scalability issues. Thickness non-uniformity, common in methods like spray coating and drop casting, can be mitigated through laser thinning114 or atomic layer etching118, though these techniques are also limited in large-scale production. Therefore, while post-processing can resolve certain limitations, others, such as misalignment, cannot be completely eliminated and continue to hinder the overall performance of 2D films. Addressing these challenges necessitates not only the development of advanced post-treatment methods, but also innovative deposition and exfoliation techniques that can overcome inherent material limitations.

Cost implications and scalability challenges of solution-processed 2D films

Although solution processing holds great promise for the fabrication of 2D materials, offering advantages such as low-temperature deposition, flexibility, and compatibility with various substrates. Several intrinsic challenges still hinder cost efficiency and scalability, particularly for large-scale industrial applications in electronics.

A primary concern is the inconsistency in material quality and uniformity. Liquid exfoliation often yields nanosheets with varied flake sizes and thicknesses, resulting in non-uniform films72,84,123,124. This necessitates additional sorting and post-processing steps to achieve desired electronic properties, increasing the operational cost. For example, purification processes like centrifugation or filtration are required to formulate dispersions, leading to increased material waste and production costs. The use of high-boiling-point organic solvents, such as N-methyl-2-pyrrolidone and dimethylformamide, compounds the issue61,62,68. While essential for good nanosheet dispersion, the management of these toxic solvents, including recovery and addressing potential surface contamination, adds complexity and cost. Moreover, solvent residue can degrade device performance51,68,84,123, necessitating further cleaning or high-temperature annealing, which negates some low-temperature processing benefits.

Scalability presents another significant barrier to industrial adoption. Film deposition methods like spin coating, inkjet printing, and Langmuir-Blodgett assembly struggle to maintain uniformity and precise nanosheet alignment when scaled to larger substrates. Achieving consistent film coverage over wafer-scale areas often leads to thickness variability and defects, degrading device performance and yield91,123,125. In large-scale manufacturing, these inconsistencies translate to reduced throughput and higher defect rates, increasing per-device costs.

Furthermore, the deposition rates of solution-processing techniques are relatively low compared to CVD method, making them less efficient for high-throughput production. Roll-to-roll printing and spray coating have been proposed as scalable alternatives, but these methods struggle to deliver the fine control needed for electronic-grade films32. Ensuring the consistent electrical performance of devices fabricated with solution-processed materials remains a challenge, as device-to-device variation is a common issue.

Overall, the inherent challenges of solution processing—material inconsistency, solvent management, and large-scale uniformity issues—significantly affect both the cost and scalability for industrial adoption. Overcoming these barriers requires innovations in processing techniques, ink formulation, and film deposition that can reduce costs while maintaining solution processing benefits. Addressing these challenges is critical for the integration of solution-processed 2D materials into high-performance electronic devices.

Solution-processable 2D devices for logic, memory, and sensing applications

As discussed in Section “Materials synthesis and deposition”, the persistent and progressively advancing endeavors within the materials chemistry and engineering domain have given rise to an extensive collection of liquid-exfoliated 2D nanosheets, ranging from semiconductors to metals and insulators. Building upon this foundation, this section explores the remarkable advancements in solution-processable 2D electronic devices in sensing, memory, and logic applications.

Properties and applications of 2D dispersions

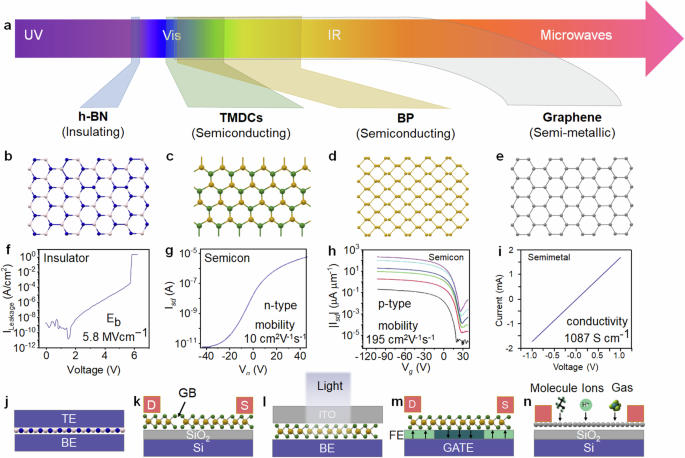

Figure 4 provides a comprehensive illustration of the crystal structures, optical absorption range, electrical characteristics, and device applications of four key types of 2DMs: h-BN, TMDCs, BP, and graphene. These materials are chosen due to their complementary electronic properties and broad bandgap ranges, making them promising building blocks for constructing sensor, storage, and logic devices. As an insulator with a wide bandgap (~6.0 eV), h-BN has an atomically smooth surface and exceptional thermal and chemical stability, making it an ideal gate dielectric for high-mobility 2D logic devices and switching layer for memristors (Fig. 4a, b, f, j). The h-BN nanosheets preserve their excellent intrinsic insulating performance even after being processed into thin-film. Indeed, the h-BN nanosheets film achieves a high breakdown strength of 5.8 ± 0.5 MV/cm126, low leakage current of (3times {10}^{9}{rm{A}}/{{rm{cm}}}^{2}) (at 2 MV/cm) and high capacitance of (245pm 5{rm{nF}}/{{rm{cm}}}^{2}), which is notably close to their bulk counterparts. These attributes make them valuable for large-scale low power transistors. Pioneered by Lanza’s and Akinwande’s work127,128,129,130, h-BN is also widely adopted as a robust switching medium in memory devices. The one-atom-thin h-BN nanosheets provide memristive devices with ultimate vertical scaling down to 0.33 nm and sub-pA operation current with femtojoule per bit energy consumption130.

a Optical portion of the electromagnetic spectrum in UV, visible, and IR range. Molecule structure and corresponding electrical properties of insulating h-BN (b, f), semiconducting n-type TMDCs (c, g), semiconducting p-type BP (d, h), semi-metallic graphene (e, i). j–n Device applications of solution-processable 2D materials. j RRAM. k Memtransistor. l photodetector. m Ferroelectric field-effect transistor (FET). n Sensor. Panel g reprinted with permission from ref. 65., Springer Nature Limited; Panel h reprinted with permission from ref. 67., Wiley-VCH2021; Panel f reprinted with permission from ref. 126., American Chemical Society; Panel i reprinted with permission from ref. 133., Wiley-VCH2021.

Semiconducting TMDCs with desirable bandgaps, such as monolayer MoS2 (1.8 eV) and WS2 (2.1 eV), MoTe2 (1.1 eV) and WSe2 (1.7 eV) represent a compelling class of materials for various electronic applications. These 2DMs consist of layers of transition metal atoms sandwiched between chalcogen atoms, forming a hexagonal lattice structure (Fig. 4c). The unique atomic arrangement in TMDCs gives rise to an unprecedented layer-dependent electronic structure, where a transition happens from an indirect bandgap in bulk to a direct bandgap in monolayer, a feature not seen in traditional bulk semiconductors. This change in band structure results in strong light-matter interaction, rendering them promising candidates for photonics and optoelectronic devices (Fig. 4l). With sizable band gaps and high mobility, TMDCs especially MoS2 and WS2, are excellent candidates for logic gates to provide high-switching speed with low power consumption. Through solution processing, their nanosheets have demonstrated decent mobility ranging from 1 ~ 10 cm2V−1s−1 and a large on/off ratio (106) in thin film transistor arrays (Fig. 4g)39,65. Most solution-processed TMDCs show electron transport behavior due to the chalcogenide vacancies introduced during the exfoliation. BP, another representative 2DM with puckered structure and anisotropic electronic properties, offers hole conduction with excellent mobility of around 200 cm2V−1s−1(Fig. 4d, h)67. Those complementary metrics offered by TMDCs and BP meet the requirement for logic gate applications, and enable basic sensors for light, pressure and chemicals (Fig. 4n). When coupled with a ferroelectric HfZrO switching layer131,132, the semiconducting 2DMs FET enables ferroelectric polarization switching with a high on/off ratio and negligible degradation in endurance and retention properties for non-volatile multilevel data storage (Fig. 4m). In addition, analogous to the grain boundaries-assisted resistive switching (RS) in CVD-grown 2D film, the edge defects of the liquid-exfoliated 2D nanosheets, facilitate ion’s interlayer diffusion in conductive filament, and thus present an efficient way for the modulation of RS characteristics33 (Fig. 4k).

Graphene, composed of a single layer of carbon atoms arranged in a hexagonal lattice, has attracted significant attention for its exceptional properties, making it a widely studied material in recent decades (Fig. 4e). The carbon atoms in graphene are characterized by sp2 hybridization. This configuration results in three localized σ bonds on the flat surface and a delocalized π bond perpendicular to it. Ideal monolayer graphene exhibits a semi-metallic nature with zero bandgap, arising from the symmetry of the honeycomb lattice at the k-points of the Brillouin zone. Consequently, graphene possesses the capability to absorb a broad range of light, spanning from ultraviolet (UV) to infrared (IR) wavelengths. A recent study highlighted the impressive electrical conductivity of 1087 ({rm{S}}cdot {{rm{cm}}}^{-1}) in exfoliated monolayer graphene nanosheets, achieved through the ammonium intercalation-based method (Fig. 4i)133.

Thin-film transistors

As shown in Fig. 5a, the evolution of solution-processable 2DM transistors shows a progressive trajectory from proof-of-concept single flake devices to wafer-scale devices and further extension to integrated circuits. For instance, MoS2 monolayers and few layers have been exfoliated in Na2SO4 aqueous solvent with large lateral size up to 50 µm134. Despite apparent limitations, including anodic oxidation by oxygen-containing radicals and possible phase transition induced by Na+ doping, individual FET made of these exfoliated MoS2 monolayers exhibit a high on/off ratio over 106 and a reasonable mobility of 1.2 cm2V−1s−1. Building upon this, pioneer work has been further reported to fabricate printed transistors consisting entirely of 2D nanocomposites, where liquid-exfoliated h-BN, graphene and TMDCs nanosheets serve as the dielectric, contact and semiconducting switching layer, respectively 90. However, broad thickness distribution due to the low yield of direct liquid exfoliation causes the printed 2D networks to have large disorder and high porosity (43–63%), resulting in poor charge transfer and low mobility of 0.1 cm2V−1s−1. Enabled by enhanced intercalation chemistry with the organic quaternary ammonium molecules, phase-pure few-layered MoS2 nanosheets with narrow thickness distribution are obtained with improved exfoliation efficiency65. The resulting thin-film transistor (TFT) arrays show a current modulation of >105 and a high mobility of 10 cm2V−1s−1. Furthermore, functional logic gates and computational circuits, including inverter, NAND, NOR, AND and XOR gates, and a logic half-adder have been demonstrated based on the MoS2 n-FET. This work opens a scalable pathway to high-performance logic applications using solution-processable 2D semiconductor dispersions. Subsequently, the solution-processed FETs are further extended to WSe2 and WS2 on both rigid and flexible substrate processed at low temperature ( < 120 °C) through Langmuir−Schaefer deposition41. The ionic-gated WS2 and WSe2 transistors show electron conduction and ambipolar conduction, respectively, with high mobility in the range of 2–16 cm2V−1s−1. However, to enable complementary integrated circuits, p-type 2D FET is necessary but challenging due to lack of stable p-type 2D semiconducting dispersions and controllable doping method, especially in solution. Therefore, a wet chemistry doping strategy has been developed by bromide molecule (Br2) treatment, where the empty Br2 ({{rm{sigma }}}_{p}^{* }) antibonding molecular orbital state introduces a shallow acceptor state of 0.08 eV above the valance band maximum of WSe235. The Br2-doped WSe2 FET shows an improved hole mobility of 27 cm2 V−1 s−1, on/off ratio of over 107 and a near-zero threshold voltage. 2D CMOS inverter composed of solution-processed MoS2 n-FET and WSe2 p-FET has been further demonstrated, showing a record high gain of 1280 at a drive voltage of 7 V. To achieve large scalability without sacrificing their performance, a commercial slot-die printing has been utilized to deposit semiconducting MoS2 layer and a unique dielectric layer, sodium-embedded alumina on 5-inch wafer125. The MoS2 FETs exhibit a record-high mobility of 80.0 ± 11.0 cm2 V−1 s−1, contributed by effective van der Waals sheet-to-sheet contacts of MoS2 nanosheets, the high capacitance as well as an energetically flat dielectric layer composed of sodium-embedded alumina.

a Solution-processed 2D logic devices which evolves from exfoliation of monolayer 2D nanosheets to wafer-scale 2D devices and logic circuits (top panel). From left to right in Panel a reprinted with permission from ref. 134. American Chemical Society; ref. 65. Springer Nature Limited; ref. 35., Wiley-VCH2021 and ref. 125. Springer Nature Limited. b Solution-processed 2D memory devices which witness an evolution from individual planar RRAM to wafer-scale arrays and 3D stacking (middle panel). From left to right in Panel b reprinted with permission from ref. 83. Springer Nature Limited; ref. 138. Wiley-VCH2021; ref. 143. Springer Nature Limited; ref. 33. Springer Nature Limited. c 2D materials-based sensors develop from simple sensing towards multifunctional flexible and stretchable capabilities, enabling smart sensing, embedded intelligence, as well as sensing-memory-computing fusion (bottom panel). From left to right in Panel c reprinted with permission from ref. 239. American Chemical Society; ref. 160. American Chemical Society; ref. 91. Wiley-VCH2022; ref. 165. AAAS. To be noted, the depicted timeline in the figure does not adhere to a one-to-one correspondence with the milestones of the key devices. Rather, it serves as a visual representation of the temporal progression from 2014 to 2024, highlighting significant milestones associated with the key devices. The alignment of these milestones along the timeline is intended to illustrate their relative importance and impact within the broader timeframe.

Resistive Random Access Memory (RRAM)

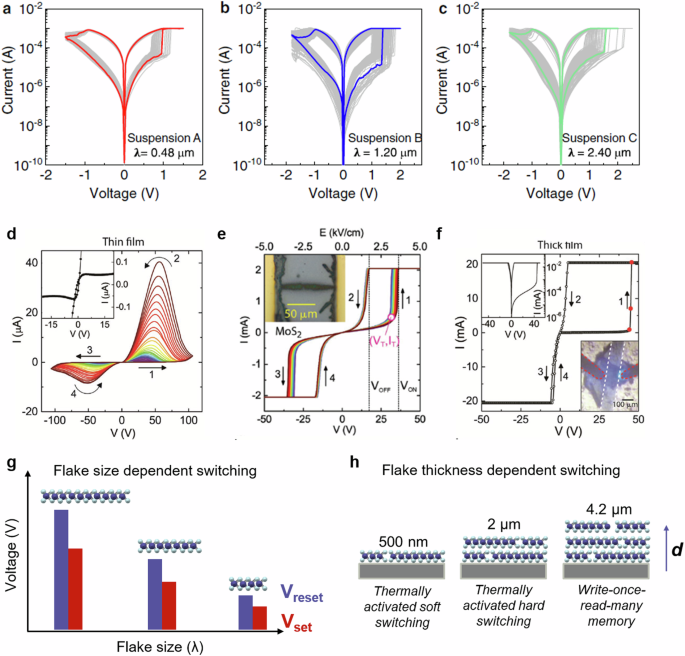

RRAM stands as a promising candidate for next-generation non-volatile memory devices, offering remarkable speed, endurance, and energy efficiency. The integration of solution-processable 2DMs plays a pivotal role in advancing RRAM technology, unlocking new opportunities for memory applications that exhibit outstanding performance while being cost-effective and compatible with the CMOS technique. Figure 5b summarizes the evolution of solution-processable RRAM. Previous investigations primarily revolved around resistive switching in graphene oxide nanosheets as active layers, either in isolation or in combination with polymers or reduced graphene oxides135,136,137. However, most of those studies only focus on the device fabrication without much concern on the performance enhancement, showing limited optimization window between endurance ( < 103 cycles), switching voltages (1 ~ 6.7 V) and memory retention ( < 104 s). Furthermore, a comprehensive understanding of the underlying switching mechanism is lacking. In this context, a novel approach utilizing solution-processed MoOx/MoS2 and WOx/WS2 heterostructures, sandwiched between two printed silver electrodes demonstrates significant breakthrough83. Schottky junction formed between the ultrathin oxide layer ( < 3 nm) and Ag interface is identified as an effective means for modulating resistive switching in the printed heterostructure RRAM. This configuration allows for an exceptionally low operating voltage of 0.2 V, an unprecedentedly dynamic resistance ranging from 102 to 108 Ω and the capability for multilevel operation. Time-dependent and temperature-dependent I–V measurement of the MoOx/MoS2 RRAM reveals that nanoionics transport in the oxide layers dominates the memory effect, where the oxygen vacancies migration causes the metal valence change between Mo6+ and Mo5+. Inspired by the printed 2D memristors, diverse solution-processed 2D materials and heterostructures have been studied for resistive switches, including TMDCs-based RRAM33,37,42,138,139, BP-based RRAM52,140 and MXene-based RRAM141,142 et al. Among them, the solution-processed TMDCs-based RRAMs stand out due to their stable chemistry and facile processability. Several milestones have been achieved with solution-processed 2DM RRAMs, e.g. large memory window ranging from 102–108 136, ultralow programming voltage down to 0.18V38, minimal switching energy of 2.6 pJ/bit and forming-free operation143. However, most of these reports focus only on individual devices without indication of device-to-device variation and circuit demonstration at large scale. Recently, the wafer-scale implementation of RRAM arrays has been demonstrated with spin-cast MoS2 nanosheets33. In-depth materials study and electrical measurement of the MoS2 nanosheets have provided physical insights into the underlying switching mechanism in the solution-processed MoS2 RRAM, where a unique inter-flake sulphur vacancies percolation causes the formation and rupture of conductive filaments. This represents an effective way for resistive switching modulation since the percolation path of sulphur vacancies can be controlled by the nanosheets geometry. This is also supported by the aerosol jet-printed WSe2 RRAM143, which shows well-preserved resistive switching with inert and non-mobile carbon-based electrodes rather than active Ag or Cu electrodes. This suggests that the resistive switching mechanism is intrinsic to the WSe2 switching layer, likely due to selenium vacancies. A detailed discussion regarding the charge transport mechanism can be found in Section “Physical insights into the charge transport mechanism in solution processable transistors, RRAM and sensors”. In addition, the spin-cast MoS2 nanosheets exhibit a high degree of plane-to-plane alignment, ensuring efficient charge transport and structural integrity. Benefiting from the robust structure and edge defect-assisted switching, the wafer-scale MoS2 memristor arrays demonstrate excellent endurance (107 cycles), long memory retention (10 years), low device variations, and a high analog on/off ratio33.

Apart from performance gains from vertical stacking of logic and memory units, the emerging RRAM devices described in the above section can be employed to compute and process data within the memory. This way of computing inspired by the parallel processing, low power consumption and adaptability of human brain is referred broadly as neuromorphic computing. Specifically, the physical property of the switching layer and its conductance modulation are exploited to mimic the synaptic property. On the device level, high performance including low switching energy is essential, else the energy savings from in-situ computation cannot be fully reaped. It is the atomically thin structure of 2D materials that makes them beneficial for neuromorphic devices—voltage scalability resulting in reduced power consumption and gate tunability leading to a greater number of analog states. In this regard, the recently reported implementation of spiking neural network with 2D–CMOS hybrid microchips using hBN as the active switching layer by Zhu et al. offers great promise129. Additionally, the synaptic properties of RRAM can be modulated by a combination of electrical and optical stimuli, resulting in enhanced data storage capability and allowing for the convergence of storage and computation with image sensors144,145. Notably, a compact, low power pixel sensor using MoS2 phototransistor146, a large-scale robust image sensor matrix with active pixels consisting of nanoporous MoS2 phototransistors147, an optoelectronic memory device enabled by tellurium-based 2D van der Waal structure for in-sensor reservoir computing148are some of the recently reported works.

Photodetector

Photodetectors are indispensable components of modern technology, enabling the conversion of light into electrical signals for applications in optical communication (where light signal serves as the carrier of encoded information) and remote sensing (where the light signals convey valuable data). Commercial photodetectors are mainly constructed from Si or Si-based compounds or III-V materials (e.g. GaAs and InGaAs)149,150. Unfortunately, Si has an indirect bandgap of 1.1 eV, which constrains the response range between 300 and 1100 nm. While the integration of III-V compound semiconductors with Si extends the photo response range towards the short-wavelength infrared (SWIR) spectrum, the fabrication processes for high-quality III-V materials are complicated, costly, and incompatible with the CMOS process. More importantly, the rigid nature of crystalline silicon, GaAs, and InGaAs semiconductors restricts their use in next-generation flexible and wearable electronics. Therefore, it is imperative to explore novel photoactive semiconductor materials that can overcome these limitations.

The introduction of 2DMs represents a transformative breakthrough in photodetector design, driven by their unique electronic and optoelectronic properties. These atomically thin materials exhibit quantum confinement effects, allowing for tunable bandgaps and remarkable photoresponsivity across a wide range of wavelengths151,152. In comparison to traditional production methods like mechanical transfer and CVD growth, the convergence of solution processing techniques with 2DMs opens new avenues for creating large-scale, cost-effective devices suitable for applications ranging from consumer electronics to industrial monitoring84,153,154,155. Diligent work has been undertaken to tailor and optimize various solution-processed 2DMs, a notable endeavor that involves engineering materials specifically matched to distinct spectral ranges. For example, graphene has an ultra-wide spectral range spanning from UV to THz frequencies, ultrafast carrier mobility ( ~ 200,000 cm2V−1 s−1), and high electrical conductivity. However, the gapless nature of graphene leads to a high dark current, significantly degrading its sensitivity and limiting the further development of graphene-based photodetectors. Consequently, other 2DMs, such as TMDCs and BPs have been investigated because of their tunable bandgap ranging from 0.3 eV to 2.0 eV, which enables high sensitivity in the visible and near-infrared (NIR) regimes155,156,157,158.

For example, photodetectors composed of individual MoS2 monolayer and few-layer flakes can achieve high photosensitivity up to 880 A/W at low illumination power156, fast response of 70 µs157 and high sensitivity of 7.7 × 1011 Jones159 in the 400–700 nm wavelength range. Coupled with their extremely low noise equivalent power, MoS2 can be an ideal candidate for very low-level photo detection. However, early works on solution-processed MoS2 photodetectors show degraded photoresponsivity and sensitivity. For instance, the inkjet-printed MoS2 photodetector has been reported with maximum photoresponsivity of 50 mA/W160. The low photoresponsivity is possibly due to the residues from the polymer stabilizer and randomly aligned nanosheets, which hinder charge transport in the device. Additionally, the use of toxic solvent dimethylformamide, which has a high-boiling point in the exfoliation of the MoS2 nanosheets, requires time-consuming and expensive formulation process or relatively high temperature to dry, constraining the range of compatible substrates. To avoid the use of toxic solvent and polymer binders in the ink, water-based and biocompatible 2D crystal inks93 have been developed for a range of 2DMs dispersions, including MoS2, WS2, h-BN and graphene, allowing the further fabrication of all-inkjet-printed graphene/WS2/graphene vdW photosensors93. However, water with a high surface tension of around 70 mN/m, exhibits poor wettability on common substrates such as Si/SiO2, glass and polyethylene terephthalate after deposition, resulting in non-uniform material deposition. This highlights the importance of formulating the ink properties to improve film quality for high-performance photodetectors. Binary solvents composed of isopropyl alcohol and 2-butanol have been developed that enables uniform deposition of BP nanosheets on PET and glass substrate without the need for substrate pre-treatment53. The binary solvent mixture creates variations in solvent proportions across the droplet due to differing evaporation rates, with faster evaporating solvent concentrated at the center and slower evaporating solvent at the edges. This results in a temperature gradient and subsequent recirculation of Marangoni flow, preventing coffee ring formation and ensuring uniform material deposition. Therefore, the BP-based photodetectors achieved an improved responsivity of 164 mAW−1 with a broadband detection range from visible to near-infrared wavelengths.

Apart from optimization over the ink properties and individual flakes, further efforts have been made to develop vdW heterostructures for high-performance and broadband photodetectors beyond the current state-of-the-art photodetectors91. VdW heterostructures offer precise control over the choice of materials in different layers, allowing for the fine tuning of electrical and optical properties to meet specific requirements, such as multispectral sensing and processing. Extensive research into various vdW photodetectors161,162,163,164 have yielded exceptional performance metrics, including ultra-high responsivity, sensitivity, and remarkably broad spectral response. Nevertheless, the construction of vdW heterostructures from solution is still in its infancy stage. Recently, an all-solution-based process for wafer scale electronics based on lateral and vertical vdW heterostructures have been reported91. Enabled by the high yield of electrochemical exfoliation, atomically thin graphene, MoS2 and HfS2 nanosheets have been produced and stabilized in a low-boiling point alcohol. Those nanosheets are further assembled into lateral and vertical vdW heterostructures in a three-terminal transistor configuration, where graphene and MoS2 serve as contact electrode and semiconducting channel, respectively. For the dielectric layer, a high temperature annealing process at 500 °C under ambient conditions transforms the HfS2 thin film into a flat HfO2 layer with significantly reduced roughness. Notably, the wafer-scale transistor array exhibits record-high photoresponsivity ( ~ 7×105 AW−1), outperforming most of the previously reported TMDC-based photodetectors156.

Moreover, the unique advantages offered by solution-processed 2D thin films extend far beyond the realm of photodetectors, exerting a transformative influence on a wide range of sensing applications, particularly within the context of the Internet of Things. In this dynamic environment, the attributes of solution-processed 2D thin films find a harmonious fit. As reported by Yan et al. 165, the absence of bonds between MoS2 nanosheets in vdW interfaces allows them to slide and rotate, resulting in remarkable mechanical flexibility, stretchability, and malleability. The staggered nanosheet arrangement also forms nanochannels, providing great permeability. These ultra-thin ( ~ 10 nm) and robust films can perfectly conform to soft biological tissues, adapting to microscopic surfaces and seamlessly integrating with living organisms. This leads to conformal interfaces that enable electronic functions within living organisms. In contrast, freestanding polycrystalline MoS2 thin films grown by CVD show poor flexibility due to stiff and strong covalent bonding within the grains and disordered bonds at their grain boundaries165. The exceptional adaptability of solution-processed MoS2 film empowers sensing devices to seamlessly conform to diverse physical environments, thereby enhancing their ability to capture accurate and reliable data. Furthermore, the capacity of solution-processed 2D thin films to maintain structural stability even in an ultrathin freestanding format offers a promising avenue for future monolithic 3D electronics. Traditional electronic devices often encounter challenges in integrating with complex geometries, limiting their potential for compact and efficient designs. Solution-processed 2D thin films, on the other hand, hold the potential to revolutionize this landscape. Their ability to conform to intricate shapes, combined with efficient charge transport across interfaces, opens the door to innovative designs that were previously constrained by the limitations of conventional materials.

Physical insights into the charge transport mechanism in solution processable transistors, RRAM and sensors

Through our previous discussions, we have unveiled the significant potential of solution-processable 2D materials and their diverse applications in logic, memory, and sensing. This section emphasizes the need for a deeper understanding of these materials, particularly their charge transport mechanisms of transistors, RRAM and sensors. Such understanding is pivotal for their overall performance, as 2DMs with different morphologies is required to address the conflicting charge transport attributes for logic and memory. Notably, transistors should be optimized for high performance and low leakage, while RRAM should be optimized for low-voltage defect-enabled switching ability. Regarding sensors, the percolating-film photodetectors provide unique opportunities to study and harness the interactions between light and the ley properties of solution processed films such as vacancies at the flake edges, lateral flake size and thickness. By employing a combination of materials characterization, we aim to shed light on the physical mechanism underlying the remarkable properties of these devices. Such understanding is critical, as it not only contributes to a fundamental understanding of these materials, but also holds the key to optimizing their performance across various applications.

Charge transport mechanism in solution-processed transistors

While extensive research has been devoted to understanding the conduction mechanism in isolated 2D flakes166,167, it becomes more complicated in the case of solution-processed transistors. The complexity arises from the interplay of multiple physical processes—a consequence of the disordered and polycrystalline nature inherent to the nanosheet networks. As discussed in Section “Materials synthesis and deposition”, the solution-processed 2DM composite film comprises disordered nanosheet networks connected via junctions of narrow vdW gap with some degree of in-plane alignment. At a mesoscopic level, the electronic conduction in these films involves contribution from nanosheet resistance (RNS) as well as the junction resistance (RJ) (Fig. 6a). While RNS is a material-dependent property, RJ is attributed to the inter-flake resistance at the overlap region between two flakes and thus is dependent on the quality and morphology of the junction. Consequently, the limiting factor for conductivity is dependent on the relative magnitude of RNS and RJ, which allows us to describe two conduction regimes of operations—junction-limited conduction (RJ »RNS) and material-limited conduction (RJ «RNS)123. Efforts to characterize and quantify the local junction resistance using conductive atomic force microscopy (C-AFM) current mapping have been reported (Fig. 6b). For instance, Nirmalraj et al. 168 investigated the junction resistance between the flakes in a solution-processed graphene film. As the C-AFM cantilever traces the junction between the flakes, the current map indicates a high voltage drop across the flake intersection. The corresponding junction resistance is found to be ∼550 Ω and ∼6.5 kΩ for a network of monolayer and multilayer graphene, respectively168. On the other hand, to investigate the intra-flake properties such as photoconductivity dynamics, optical-pump terahertz (THz)-probe spectroscopy is widely employed (Fig. 6c)169. Owing to the transient nature of THz pulses, the optical excitation injects charge carriers that are driven over a short distance (tens of nm), thus capable of unveiling properties of intra-flake transport. Additionally, the temperature-dependent photoconductivity analysis offers an effective way to deconvolute the contribution of intra-flake properties from the total conductivity169. As shown in Fig. 6d, the photoconductivity of MoS2 nanosheets increases as the temperature is reduced, indicating that the intra-flake transport characteristics are dominated by phonon scattering limited band-like transport169.

a Schematic representation of nanosheet network as a resistive network comprising of nanosheet resistance (RNS) and junction resistance (RJ). b C-AFM is employed to map the junction resistance via current mapping across the inter-flake junction. c Schematic illustration of optical-pump–THz-probe spectroscopy on 2D material systems. d Photoconductivity dynamics of MoS2 nanosheet using THz pump-probe spectroscopy under different temperatures. Reprinted with permission from ref. 168, American Chemical Society 2011. Reprinted with permission from ref. 169, Wiley-VCH2023.

As shown in Fig. 7, attempts to characterize the charge transport mechanism in solution-processed logic devices based on a combination of temperature and electric-field-dependent measurements have been reported170,171,172. Erik Piatti et al. 172 investigated the charge transport mechanism of surfactant and solvent-free inkjet-printed MoS2 films using temperature and gate dependent conductivity. As shown in Fig. 7a, inkjet-printed MoS2 transistors exhibit a gate-induced crossover from hopping at low gate voltage to band-like transport at high gate voltage. These features indicate charge transport occurring in two distinct regimes: an insulating phase characterized by hopping transport, and a metallic phase involving transport over extended states. The separation between these phases is marked by the insulator-to-metal transition at Vg = 1.37 V, governed by the ratio of intra- and inter-flake conductance. Figure 7b shows the plot of conductivity (σ) against T(-1/4) for a representative MoS2 ungated device, where the logarithm of σ scales linearly with T(-1/4) for temperatures up to 200 K, suggesting 3D Mott Variable Range Hopping (VRH) conduction. Similar transitions from Mott VRH at low temperatures to nearest neighbor hopping (NNH) at high temperatures have been documented in disordered MoS2 flakes166,173. A benchmark plot of activation energy values observed in disordered and isolated MoS2 flakes under gated and ungated condition are shown in Fig. 7c. The notably elevated activation energy obtained in MoS2 networks suggests that the conduction is primarily dominated by inter-flake hopping.

a–c Charge transport mechanism in solvent-free 2D films. a Conductivity vs gate voltage of printed MoS2 transistors measured at different temperatures. b Conductivity as a function of T-1/4 for an ungated MoS2 device to determine the reduced activation energy. c Activation energy (Ea) as a function of gate voltage in different MoS2 devices. d–f Charge transport mechanism in covalent-interconnected 2D network film. d Schematic representation of inter-flake transport facilitated by vacancy healing mechanism and covalent interconnections in MoS2 films by aliphatic PDT and aromatic BDT molecules. e Conductivity vs temperature plot for MoS2 films, MoS2–PDT networks, and MoS2–BDT networks. f Extrapolated average Rhop for MoS2 films, MoS2–PDT networks, and MoS2–BDT networks, accompanied by an illustration of their respective hopping mechanisms. Figures a-c reprint with permission from ref. 172, Springer Nature Limited. Figures d–f reprint with permission from ref. 169, WILEY-VCH 2023.

Recently, molecular functionalization has been explored as an effective strategy to overcome limitations of high inter-flake junction resistance and disorder109,169. The functionalization serves not only to heal the disorders, but also facilitates the proximity of adjacent flakes, promoting the formation of a covalent interconnection of TMDCs. For instance, by employing multi-scale analysis, aromatic-conjugated 1,4-benzenedithiol (BDT)) versus aliphatic 1,3-propanedithiol (PDT) linkers have been investigated on MoS2 nanosheet films109,169. Primarily, through temperature-dependent scattering time analysis, the scattering rate for MoS2–BDT is found to be 40% less than pristine MoS2 films, indicating the beneficial role of the thiol group in healing vacancies. Figure 7d shows a schematic representation of the healing mechanism and covalent network interconnection in pristine MoS2 films utilizing aliphatic PDT and aromatic BDT molecules, focusing on inter-flake charge transport. According to the temperature-dependent conductivity of MoS2, MoS2–PDT networks, and MoS2–BDT networks, two distinct operational regimes are observed (Fig. 7e). In the high-temperature range (200K–340 K), the conductivity exhibits an exponential dependence on temperature, indicative of a thermally activated hopping regime. Conversely, in the low-temperature range (5 K–150 K), conductivity remains independent of temperature, suggesting a tunneling regime of operation.

The extrapolated average hopping distances (Rhop) for MoS2 films, MoS2–PDT networks, and MoS2–BDT networks, accompanied by an illustration of their respective hopping mechanisms are shown in Fig. 7f. Pristine MoS2 exhibits Efros–Shklovskii variable range hopping (ES-VRH), where the hopping transport is governed by the Coulomb scattering of the charge carriers interacting with fixed charge centers. Conversely, in MoS2–PDT networks, the sulphur vacancies are healed by the aliphatic PDT molecules, neutralizing the Coulombic scattering centers, which shifts the charge transport mechanism from ES-VRH to 3D Mott Variable Range Hopping (3D Mott VRH). In the case of MoS2-BDT molecules, the carrier dynamics is characterized by nearest neighbor hopping (NNH), where the charge carriers hop between the two spatially nearest trap sites, regardless of their energy levels. Here, the aromatic ring plays a crucial role in enhancing inter-flake transport by connecting two adjacent flakes and improving their electronic connectivity by establishing a favorable conduction path for the charge carriers. Thus, in contrast to solvent-free MoS2, the charge transport in covalent network-based MoS2 is primarily governed by an inter-flake hopping mechanism, whose characteristics are significantly influenced by the chemical structure of the linker.

These investigations emphasize the necessity for a comprehensive characterization of the charge transport dynamics throughout the nanosheet network to reveal the interplay between charge carrier dynamics across the junctions (inter-flake transport) as well as carrier transport within each flake (intra-flake transport). This is particularly crucial as inter-flake transport through hopping or tunneling across junctions can significantly affect mobility and device-to-device variability that are key to wafer-scale integration and performance reliability. Nevertheless, the investigation of charge transport properties of nanosheet networks is still in the early stage of development. The polycrystalline nature and the complexities related to ink formation and different deposition methods have posed challenges in investigating the charge transport behavior in solution-processed 2D transistors. Employing diverse techniques, including temperature-dependent, magnetic-field-dependent, and electric-field-dependent measurements, is essential to unveil the complete mechanism. Additionally, careful consideration of the contribution of disorders, such as sharp boundaries between different printed flakes, is essential.

Charge transport mechanism in solution-processed RRAM

As opposed to logic devices, where defects are detrimental to operations, defects such as sulphur vacancies in MoS2 introduced during liquid phase exfoliation, play a crucial role in the switching kinetics of memristive devices33. However, the resistive switching mechanism in solution-processed memristors remains poorly understood. Unlike crystalline or amorphous materials, resistive switching in 2D nanosheet networks is uniquely influenced by nanosheet dimensions and percolation path morphology. This is a unique characteristic potentially observed only in solution-processed thin films33. Moreover, the understanding of the switching mechanism is further complicated by the presence of electrochemically active metal electrodes. This is because the dynamics between metal ions vs vacancies transport in the active region that eventually constitutes the conductive filament remains elusive38,143. In this section, we unveil the resistive switching mechanism in solution-processed RRAM through a synergistic approach that combines in-situ material characterization and physical modelling. Such fundamental understanding of the factors that influence the resistive switching mechanism is crucial for optimizing device design and maximizing device functionality.

In-situ characterization and physical modelling

Several in-situ characterization and visualization techniques have emerged as key approaches in investigating the switching mechanism in memristive devices. The techniques reported for solution-processed memristive devices is shown in Table 1. Importantly, they provide critical information about the process of resistive switching, nanoscale morphology, constituent of conducting filament and their interfaces. Among these, in-situ conductive atomic force microscopy (C-AFM) is a versatile technique that captures local morphological, topographical changes and determine the location of conductive filament by probing the local current across the active area. Feng et al. 38 employed such C-AFM current mapping and reported that faster switching with high current density is related to defective locations within the inkjet-printed MoS2 switching medium. Additionally, in-situ Kelvin probe force microscopy (K-PFM) enables surface potential mapping and provides insights on vacancy dynamics, quantification of vacancies, trapping/de-trapping of space charge, etc. Furthermore, Tang et al. 33 employed in-situ K-PFM characterization in combination with C-AFM analysis to reveal the presence of sulphur vacancies at the flake edges of solution-processed MoS2 films and vertical percolation across the stacks. In-situ thermal imaging of filaments by an infrared video camera enables direct monitoring of device temperature and can provide qualitative insights on thermal-assisted switching174. While in-situ PL spectroscopy can characterise localized oxidation in the film during switching, dark field and bright field optical micrograph can aid in visual inspection of features in the channel including filaments and dendrites on a slightly larger spatial resolution174.

However, owing to the buried channel and inaccessibility of the active area, two terminals vertical memristors are not suitable for most of the in-situ characterization techniques such as K-PFM, C-AFM, etc. Hence visualization efforts on vertical memristors are majorly focussed on post-mortem imaging of devices which, however, fails to capture the dynamic process of defect migration. Thus, due to the limited temporal resolution, the investigation of vacancy kinetics and transportation over time (retention), repeated cycling (endurance), etc is challenging. Additionally, the spatial resolution in most of the techniques is limited to a few micrometres and is particularly a concern in solution-processed films since the percolating nanosheet network may exhibit a switching mechanism different from individual flakes.

Simulation and modelling, on the other hand, are inevitable tools that offer timely and cost-effective approaches to support the experimental investigation175,176. The demand is for a multi-scale modelling strategy that can describe the physical details of the materials as well as capture the high-level description of system-level operations. Accurate physical models can aid in the investigation of the dynamic resistive switching, providing insights on intermediate conductive filament growth/rupture mechanisms and the interplay between dominant driving forces (e.g. electrical vs. thermal) at a larger spatial and temporal resolutions than those achievable with in-situ characterization techniques. Crucially, vacancy migration and interface barrier adjustments across the percolating network, which are difficult to observe with in-situ characterization techniques, can be reconstructed with a physical model. Different modelling approaches in terms of computational cost and accuracy are summarized in Table 2.